SPI SRAM Controller XB

Description

The SPI SRAM control Xcelerator Block provides hardware control of an attached external SPI SRAM. The XB integrates an SRAM memory controller for use with a SPI-based serial SRAM chip and the Alorium SPI XB.

The associated support library for this XB offers an intuitive user interface for configuring, reading, and writing the SPI SRAM parts.

More details regarding the XB and functions that are available via the assiciated support library can be found on our GitHub page. Click here or on the button below to check it out.

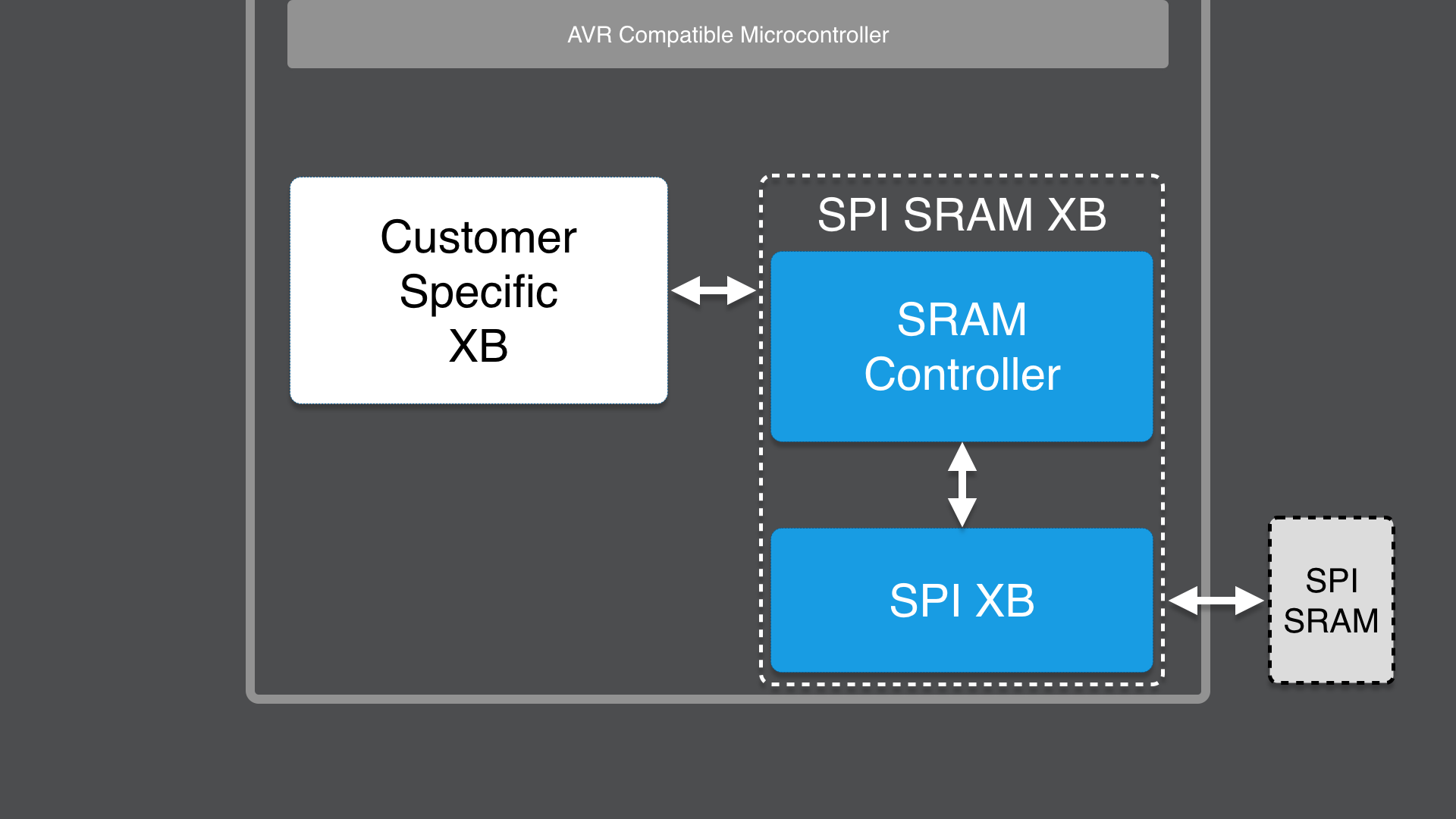

Block Diagram

The following block diagram shows an example of how the XB can be integrated with a customer-developed logic for providing access to an external memory part.

Specifications

- Configurable for Byte, Page and Sequential modes – set from software through configuration register

- Supports multiple SPI clock clock speeds (default 100, clk/2, fastest) as defined by ATMega328 spec

- Extended address mode option for SPI SRAM chips that require 3 bytes of address

Required Alorium Technology library: XLR8SPISRAM